A DSP digital signal processor is fundamentally distinct from a general-purpose CPU, primarily because its hardware is explicitly wired to calculate mathematical operations in real-time rather than simply managing system control. While a standard CPU relies on complex caching and branch prediction to run an operating system, a DSP utilizes a specialized architecture—often involving Harvard memory structures and hardware multipliers—to execute algorithms like Fast Fourier Transforms (FFT) and convolution with minimal latency. This article details exactly how these architectural choices allow DSPs to outperform CPUs in math-intensive tasks.

Architectural Efficiency in Mathematical Computation

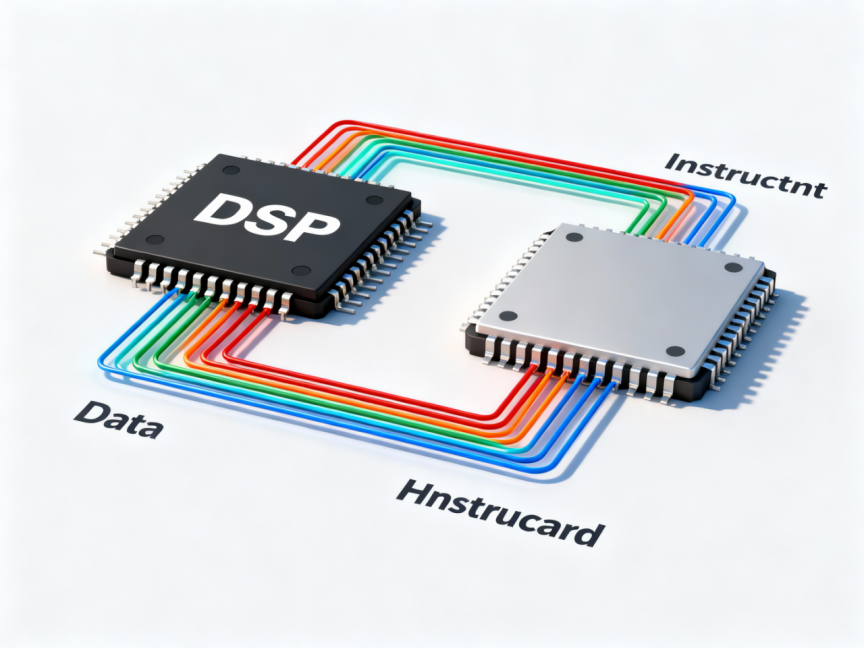

To achieve deterministic performance, DSPs abandon the flexible but slow Von Neumann architecture found in standard microcontrollers in favor of structures capable of simultaneous data and instruction retrieval.

Harvard Architecture and MAC Unit Integration

The most significant bottleneck in general-purpose CPUs is the shared bus for instructions and data, known as the Von Neumann bottleneck. A DSP digital signal processor overcomes this by employing a Harvard architecture, which features physically separate buses for program memory and data memory. This allows the core to fetch an instruction and a data coefficient in the exact same clock cycle.

Furthermore, the core of digital filtering relies on the equation A = B× C + D. In a standard CPU, this operation might require four or more clock cycles to fetch, decode, multiply, and add. In contrast, DSPs feature a dedicated hardware Multiply-Accumulate (MAC) unit. This specialized logic gate enables the processor to fetch two numbers, multiply them, and add the result to an accumulator, all within a single clock cycle. For Finite Impulse Response (FIR) filters, this single-cycle execution increases throughput by over 400% compared to standard ALUs.

Hardware-Driven Addressing and Looping

Beyond raw calculation, data management is critical. Algorithms like the FFT require data to be accessed in bit-reversed order, a process that consumes significant software overhead on a standard CPU. DSPs utilize hardware-accelerated address generation units (AGUs) that automatically calculate these complex addresses in the background.

Additionally, digital signal processing DSP tasks often involve loops with thousands of iterations. Standard CPUs waste clock cycles checking “if-then” branch conditions and updating loop counters. DSPs implement zero-overhead looping, where dedicated hardware registers manage the loop count. This eliminates branch control latency entirely, allowing the pipeline to remain saturated with valid data processing instructions 100% of the time.

Optimizing Real-Time Data Latency and Flow

While computational speed is vital, the ability to move data from peripherals to the core without introducing jitter is what defines a true real-time system.

Direct Memory Access and Interrupt Handling

DSPs utilize intelligent Direct Memory Access (DMA) controllers to transfer data from Analog-to-Digital Converters (ADCs) to memory without utilizing the processor core. This architecture ensures the core processor is never idle waiting for data, significantly reducing the total latency from signal input to processed output. Furthermore, unlike CPUs that require extensive cycle time to save context stacks during an interrupt, DSPs use shadow registers. These allow for near-instantaneous state saving, ensuring that high-priority signal events are handled immediately.

Application Specificity in Audio and Telecom

The impact of this architecture is evident in historical and modern applications. For instance, the legacy aiwa DSP surround digital signal processor utilized these specific hardware traits to manage multi-channel audio decoding with zero perceptible delay, a feat general CPUs of that era could not achieve. Today, engineers using advanced digital signal processing DSP software and design tools rely on these same hardware efficiencies to implement complex 5G telecommunications protocols and real-time noise cancellation, where a delay of even a few microseconds is unacceptable.

UniBetter Electronic Component Procurement Solutions

UniBetter Technology serves as a premier partner for engineers and procurement managers seeking reliable electronic component sourcing rather than manufacturing.

Global Sourcing and Quality Assurance

UniBetter distinguishes itself through a robust global supply chain network designed to locate hard-to-find, obsolete, or high-demand integrated circuits and microprocessors. The company does not manufacture chips but provides a critical service in the electronics ecosystem by ensuring 100% authenticity through rigorous quality inspection systems.

Cost Reduction and Supply Chain Efficiency

For businesses facing supply chain disruptions, UniBetter offers professional procurement services that help lower costs and shorten lead times. Their expertise in electronic part procurement solutions allows clients to secure essential DSPs, MCUs, and analog components without the risk of counterfeit parts. By leveraging a global network of over 1,000+ audited premium suppliers,UniBetter ensures that production lines remain active, providing a seamless bridge between component manufacturers and end-user product developers.